該系統(tǒng)可以完成圖像的采集、處理和顯示,從而實現(xiàn)目標識別與跟蹤的智能信號處理。該系統(tǒng)是對攝像機數(shù)字,模擬兩路視頻數(shù)據(jù)進行采集,處理后通過PCI總線在PC機上顯示出來。

視頻信號采集模塊

攝像機提供兩路視頻信號:一路模擬視頻,一路數(shù)字視頻。

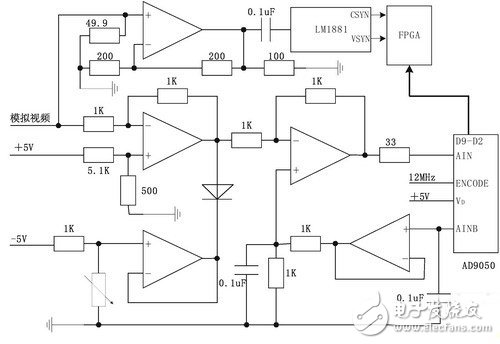

模擬視頻信號經(jīng)過鉗位校正、放大后,將信號送入到A/D轉(zhuǎn)換器,再經(jīng)FPGA鎖存后將視頻信號發(fā)送給DSP1;經(jīng)視頻同步分離電路,由LM1881分離出模擬視頻的行、場同步信號,用于控制視頻數(shù)據(jù)采集到DSP1,以便進行圖像處理。鉗位校正、視頻同步電路如圖1所示。模擬視頻經(jīng)運放輸入,將中心電平調(diào)到3.3V,加到 A/D輸入端。A/D轉(zhuǎn)換后的數(shù)據(jù)進入FPGA鎖存。運放均采用ADI公司的AD8047AR,A/D轉(zhuǎn)換器采用ADI公司的AD9050。AD9050 為10位A/D轉(zhuǎn)換器,取其高8位進入FPGA。采樣時鐘12MHz,與數(shù)字視頻信號相同。由FPGA對48MHz時鐘四分頻產(chǎn)生。

圖1 模擬視頻輸入轉(zhuǎn)換電路

攝像機的數(shù)字視頻信號為14對差分信號,經(jīng)FPGA將差分信號轉(zhuǎn)換為單端信號,并鎖存數(shù)據(jù)。每個象素14位,每幀320×240。

FPGA采用ALTERA公司的CYCLONE系列EP1C3T144C-6,配置芯片采用EPC2LC20。EP1C3T144C-6具有將差分信號轉(zhuǎn)單端信號的專用I/O口。鎖存在FPGA的數(shù)字,模擬兩路視頻信號根據(jù)工作模式選擇輸出到DSP1數(shù)據(jù)總線上,由DSP1讀入處理,數(shù)據(jù)速率與模擬視頻的采樣速率,數(shù)字視頻的數(shù)據(jù)速率相同。工作模式選擇,開關(guān)控制通過PIC9054引入到FPGA。

DSP處理器模塊

大功率電感廠家 |大電流電感工廠