目前實現(xiàn)加載的方法通常有兩種:一種是用專用Cable通過JTAG口進(jìn)行數(shù)據(jù)加載,另一種是外掛與該FPGA廠商配套的PROM芯片。前者需要在PC機(jī)上運行專用的加載軟件,直接下載到FPGA片內(nèi),所以掉電數(shù)據(jù)仍然會丟失,只適用于FPGA調(diào)試階段而不能應(yīng)用于工業(yè)現(xiàn)場的數(shù)據(jù)加載。后者雖然可以解決數(shù)據(jù)丟失問題,但這種專用芯片成本較高,供貨周期也較長(一般大于2個月),使FPGA產(chǎn)品的開發(fā)時間受到很大約束。根據(jù)FPGA芯片加載時序分析,本文提出了采用通過市面上常見的扁平型電感Flash ROM芯片替代專用PROM的方式,通過DSP的外部高速總線進(jìn)行FPGA加載;既節(jié)約了系統(tǒng)成本,也能達(dá)到FPGA上電迅速加載的目的;特別適用于在FPGA調(diào)試后期,待固化程序的階段。下面以兩片Xilinx公司Virtex-4系列X電感生產(chǎn)廠家C4VLX60芯片為例,詳細(xì)介紹采用TI公司的TMS320C61416 DSP控制FPGA芯片數(shù)據(jù)加載的軟硬件設(shè)計。

1 Xilinx FPGA配置原理

Virtex-4系列的FPGA芯片外部配置引腳MODE PIN(M0、M1、M2),有5種配置模式,如表1所列。

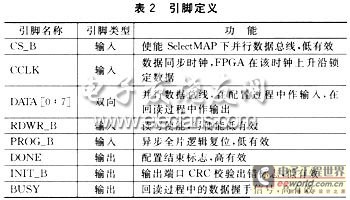

FPGA在Slave SelectMAP方式下,共用了表2所列的15個配置引腳。

1.1 配置流程

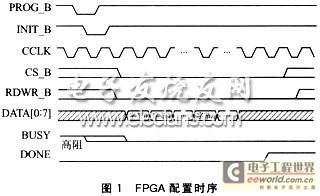

FPGA加載時序如圖1所示。各配置信號必須滿足其時序關(guān)系,否則配置工作無法正常完成。

圖1中,Slave SelelctMAP加載主要包括以下3個步驟:

①啟動和初始化。FPGA上電正常后,通過PROG_B引腳低脈沖進(jìn)行FPGA異步復(fù)位,使得FPGA內(nèi)部邏輯清零。其次PROG_B上拉高,停止外部復(fù)位,INIT_B引腳會在TPOR時間段內(nèi)自動產(chǎn)生一個由低到高的跳變,指示FPGA內(nèi)部初始化完成,可以進(jìn)行數(shù)據(jù)下載;同時FPGA在INIT_B的上升沿采樣其模式引腳MODE PIN,決定其模式配置。

②比特流加載。INIT_B信號變高后,不需要額外的等待時間,Virtex器件就可以立即開始數(shù)據(jù)的配置。比特流數(shù)據(jù)在外部CCLK信號上升沿按字節(jié)方式置入。該過程包括同步初始化字、器件ID號校驗、加載配置數(shù)據(jù)幀、CRC校驗4個部分。

③STARTUP啟動。在成功校驗CRC碼位后,比特流命令使得FPGA進(jìn)入STARTUP狀態(tài)。它是由8相狀態(tài)機(jī)實現(xiàn)的。中間包括等待DCM鎖相、DCI匹配等幾個狀態(tài),最后FPGA釋放外部DONE引腳,對外輸出高阻態(tài),由外部上拉高,指示FPGA加載成功。

1.2 文件生成

ISE生成數(shù)據(jù)文件主要有3種:BIT文件,由二進(jìn)制格式進(jìn)行表征邏輯設(shè)計,包括文件頭和配置數(shù)據(jù),主要用于JTAG下載電纜模式;MCS文件,為外部PROM燒寫生成的下載文件,ASCII碼,與前者不同的是它含有在PROM中的數(shù)據(jù)地址和校驗值;BIN文件格式,由二進(jìn)制表示,完全由配置數(shù)據(jù)組成,不需要作其他的提取和工字電感器進(jìn)制轉(zhuǎn)換,只是配置前的Byte-Swapped是在CPLD中實現(xiàn)的。本設(shè)計采用的是BIN文件格式。

2 硬件實現(xiàn)

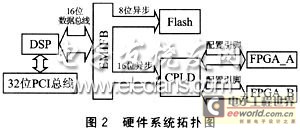

系統(tǒng)采用2片Xilinx Virtex-4系列的600萬門的FPGA XC4VLX60。主MCU是TI公司高性能定點處理器TMS320C6416,對外有2個EMIF總線接口,分別是64位寬EMIFA和16位寬EMIFB。EMIFB上掛有8位8MB的Flash和16位CPLD:Flash做2片F(xiàn)PGA的BIN文件保存,之前由仿真器燒寫;CPLD用于2片F(xiàn)PGA地址譯碼和DSP與FPGA配置部分的邏輯接口。整個數(shù)據(jù)流程是在DSP上電啟動后,Bootloader自行引導(dǎo)用戶程序運行。該程序負(fù)責(zé)由EMIFB總線搬移Flash空間中BIN文件,通過CPLD分別對2片F(xiàn)PGA進(jìn)行配置加載。硬件系統(tǒng)拓?fù)鋱D如圖2所示。

3 軟件設(shè)計

軟件包括3部分:引導(dǎo)Bootloader代碼,加載FPGA用戶程序以及接口部分的CPLD Verilog代碼。

3.1 DSP Bootloader

本系統(tǒng)中目標(biāo)板處于FPGA調(diào)試后期,需要固化其加載程序。整板上電后,要求脫離仿真器自行加載FPGA,因此這里采用DS 大功率電感廠家 |大電流電感工廠